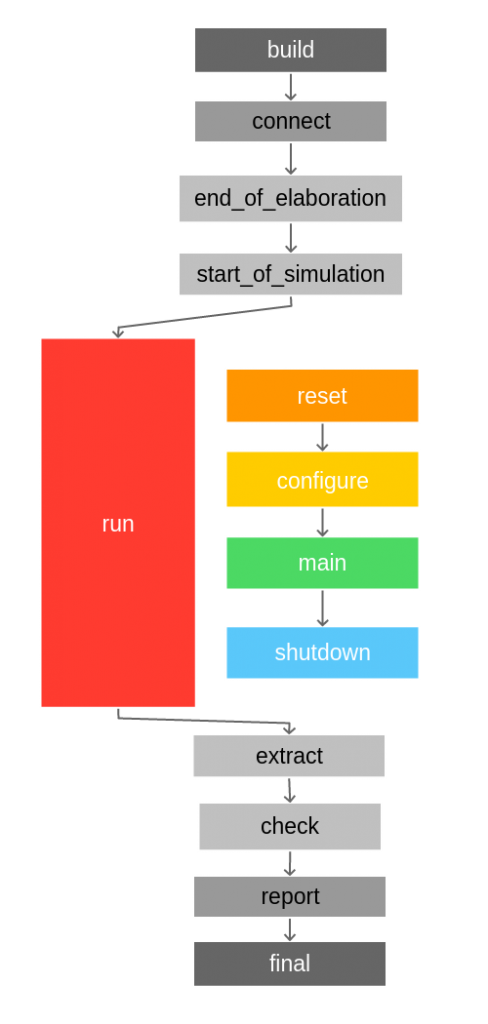

UVM introduces the concept of phases to ensure that all objects are properly configured and connected before starting the runtime simulation. Phases contribute to a better synchronised simulation and enable to the verification engineer to get better modularity of the testbench.

UVM phases consists of:

- build

- connect

- end_of_elaboration

- start_of_simulation

- run

- reset

- configure

- main

- shutdown

- extract

- check

- report

- final

The run phase has been simplified to get a better picture of how phases worked. Nevertheless, all subphases in the run phase have a pre_ and post_ phase to add flexibility. Therefore, the run phase is actually composed by the following phases:

- run

- pre_reset

- reset

- post_reset

- pre_configure

- configure

- post_configure

- pre_main

- main

- post_main

- pre_shutdown

- shutdown

- post_shutdown

Although all phases play an important role, the most relevant phases are:

- build_phase: objects are created

- connect_phase: interconnection between objects are hooked

- run_phase: the test starts. The run_phase is the only phase which is a task instead of a function, and therefore is the only one that can consume time in the simulation.

UVM phases are executed from a hierarchical point of view from top to down fashion. This means that the first object that executes a phase is the top object, usually

testbench → test → environment → agent → {monitor, driver, sequencer, etc}

Nevertheless, in the connect phase, this happens the other way round in a down to top fashion.

{monitor, driver, sequencer} → agent → environment → test → testbench