El dispositivo Cyclone IV de Altera dispone de unas memorias embebidas llamadas M9K. Estas memorias son configuradas por el sintetizador (Quartus) y dependiendo del tamaño necesario, se pueden combinar varias. Estas memorias siempre son síncronas, por lo que para que el sintenizador utilice una memoria M9K a partir del código, la memoria en cuestión debe estar gobernada por la señal de reloj.

Estas memorias pueden funcionar con un puerto puerto simple (entrada-salida) o un puerto doble. La configuración de puerto doble consiste en leer de manera independiente una misma memoria por dos puertos. Otra de los modos de funcionamiento es ROM, en el que se escribe el contenido al programar la FPGA y solo es posible leer su contenido.

Dependiendo de la configuración, la capacidad disponible las memorias M9K puede variar. Para anchos de palabra de 1, 2 y 4 bits la capacidad disponible es de 8k (8192 bits). Para tamaños de palabra mayores (8+1), (16+2), (32+4), la capacidad disponible es de 9k (9216 bits).

Las configuraciones en modo ROM son:

- 8k x 1 bit

- 4k x 2 bits

- 2k x 4 bits

- 1k x (8+1) bits

- 512 x (16+2) bits

- 256 x (32+4) bits

Las configuraciones en modo puerto doble son:

- 8k x 1 bit

- 4k x 2 bits

- 2k x 4 bits

- 1k x (8+1) bits

- 512 x (16+2) bits

En el caso de los anchos de palabra no potencias de 2, se puede utilizar estos bits extras para control de errores.

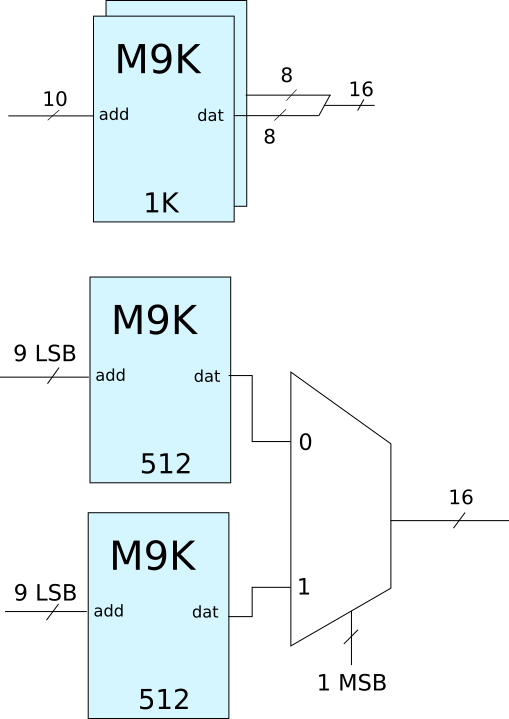

Ejemplo de memoria 1k x 16

La primera opción está más optimizada ya que se necesita menos hardware para obtener el mismo resultado.

La primera opción está más optimizada ya que se necesita menos hardware para obtener el mismo resultado.

Una joya de artículo. Me servirá mucho en el proyecto que comenzaré sobre procesamiento de imágenes.

Gracias.