Introduction

Any two-terminal network whose internal circuitry is made up solely of resistors, current sources and voltage sources can be simplified to a voltage source (\(V_{TH}\)) with a resistor in series (\(R_{TH}\)). This is called Thevenin’s theorem.

In order the find the Thevenin’s equivalent circuit, it is necessary to follow two steps:

- Find \(R_{th}\) by turning off all internal sources and connecting an external current source.

- Find \(V_{th}\) by turning on all internal sources and leaving the external current source in open circuit.

When we turn off all internal supply sources we set \(v_{int} = 0\), i.e., shorting the internal voltage supply sources, and we set \(i_{int} = 0\), i.e., opening the internal current supply sources. Then, we apply an external current supply source (\(I_{ext}\)) and compute the correspondent voltage between the two terminals (\(V_{1}\)). The value of \(R_{TH}\) will be:

\[

R_{th} = \frac{V_1}{I_{ext}}

\]

On the second step, we will turn on again all the internal sources and set the external current source as open circuit. The voltage seen at the two terminals of interest will be \(V_{th}\)

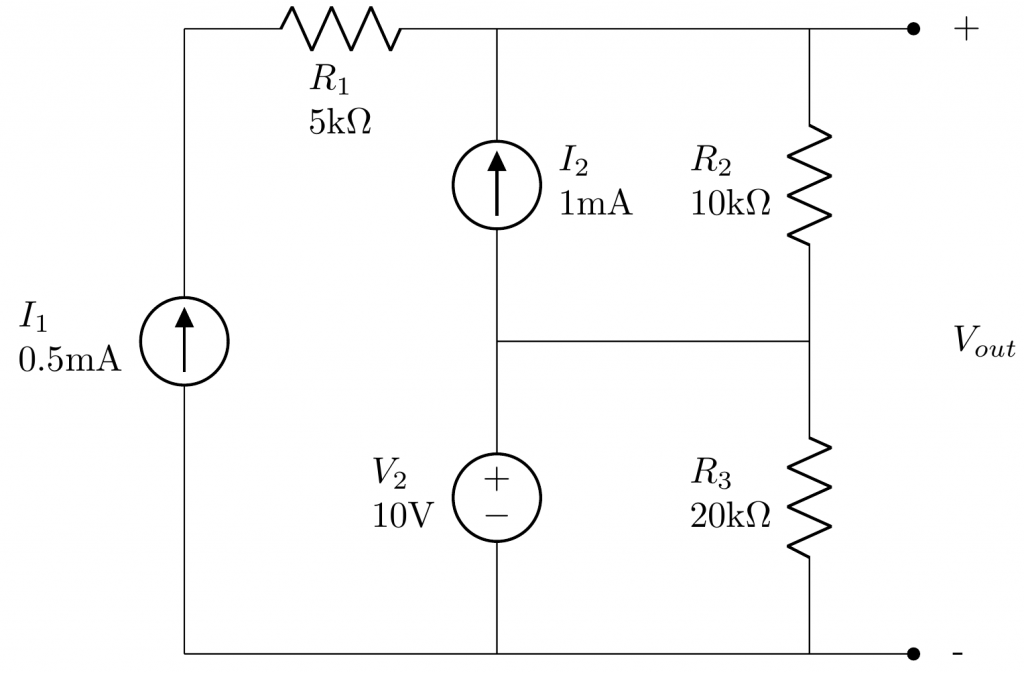

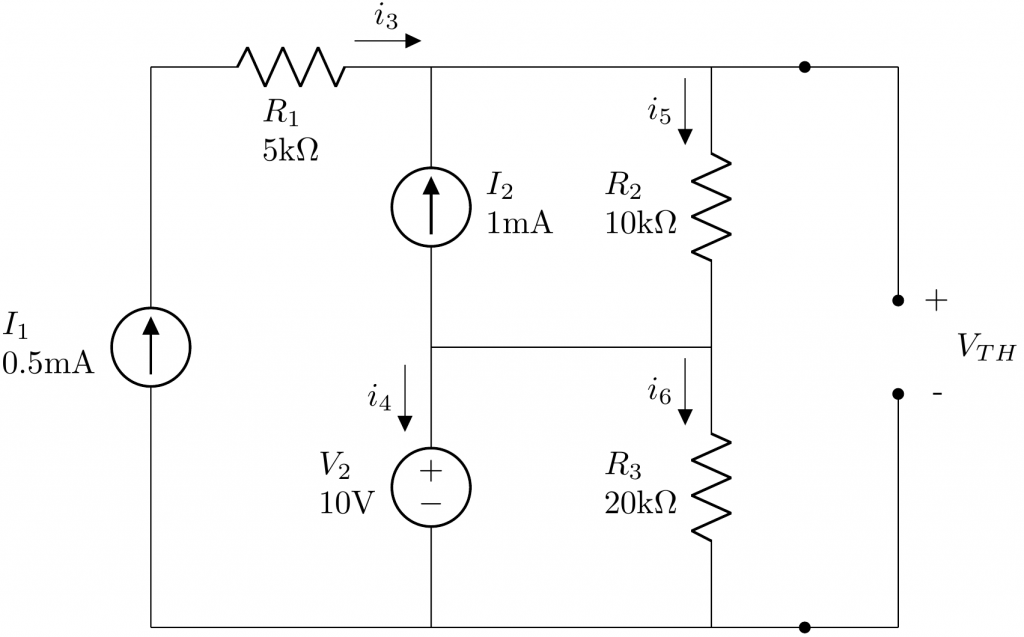

Example

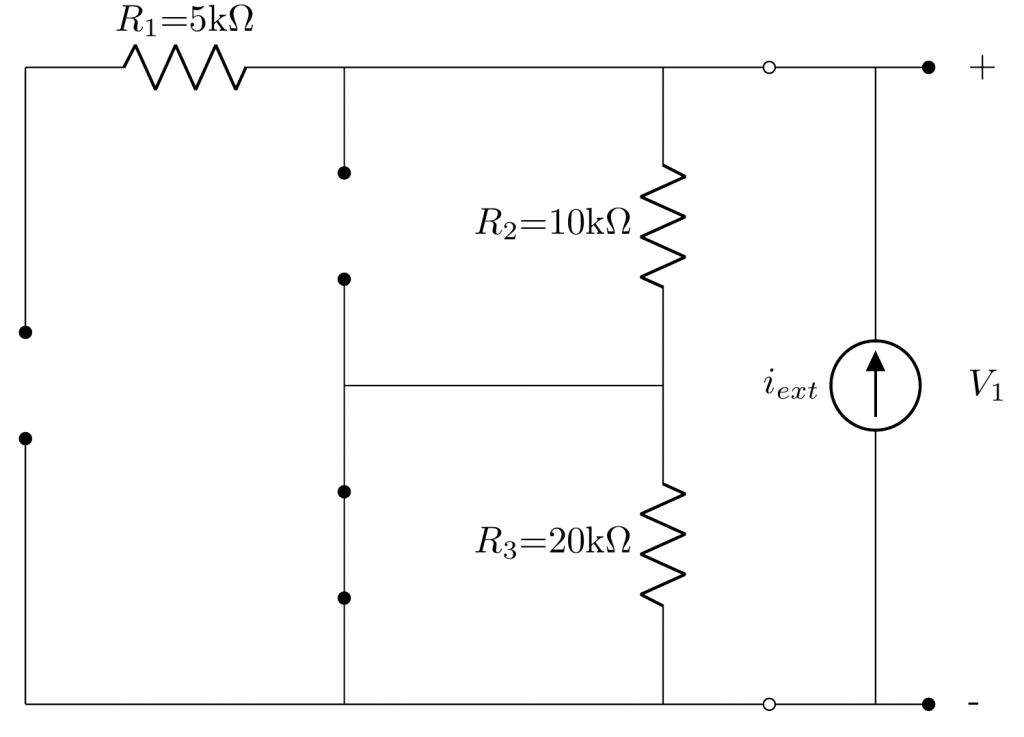

We will start the circuit analysis by setting all internal supply sources off. All the voltage sources will be shorted whereas the current sources will be left in open circuit.

From here, now we are going to compute what is the voltage \(V_{1}\).

Since there is no path to the negative terminal on \(R_1\) and \(R_3\) is shorted, they don’t contribute to the output voltage \(V_1\).

Instead, \(V_1\) can be computed as:

\[

V_1 = i_{ext} \cdot R_2

\]

Therefore, the Thevenin’s resistance is:

\[

R_{TH} = \frac{V_1}{i_{ext}} = \frac{i_{ext} \cdot R_2}{i_{ext}} = R_2

\]

Now we need to compute Thevenin’s voltage \(V_{TH}\). For this we are going to turn on again all the internal sources, i.e., leaving the circuit as it originally was, and computing the voltage across its two terminals.

If we apply the Kirchhoff’s current law (KCL) on every node:

\[

I_2 + i_3 = i_5

\]

\[

I_1 = i_3

\]

\[

i_5 = I_2 + i_4 + i_6

\]

From Equation 1, we find that

\[

i_1 + i_3 = \frac{V_{TH} – V_3}{R_2} \Rightarrow \left(i_1 + i_3\right) R_2 + V_3 = V_{TH}

\]

\[

V_{TH} = \left(0.5~mA + 1~{mA}\right) \cdot 10~{k}\Omega + 10~{V} = 25~V

\]

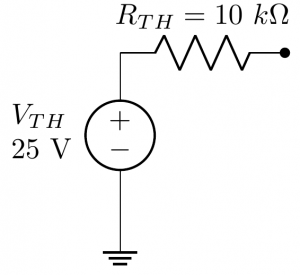

With this information, we can say that an equivalent circuit seen from these two terminals can be: